The Altium Development team are pleased to announce the 14th update for Altium Designer 10.

This release focuses on further BugCrunch requests, with some of the notable enhancements including:

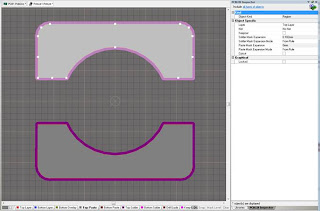

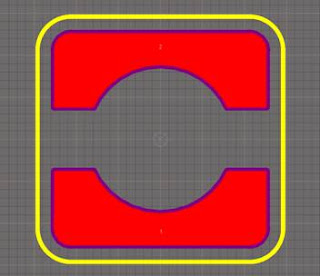

Variant support added to the STEP exporter

Now you can export mechanically accurate variants of the PCB assembly to 3rd Party Mechanical CAD tools. This will allow product enclosures and MCAD processes to be tuned to the specific needs of a design variant rather than having to accommodate all variants within a single MCAD model of the PCB design.

DXF/DWG added to Outjobs

With the addition of DXF/DWG export support in Outjobs, now you can automate the creation of this common output format and share settings across multiple projects.

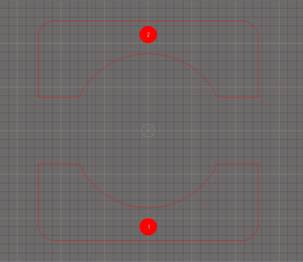

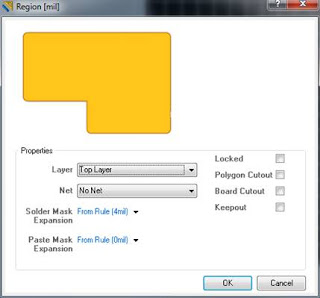

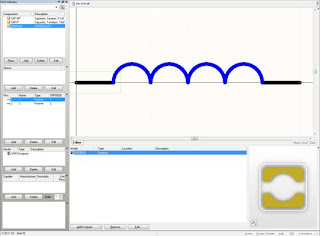

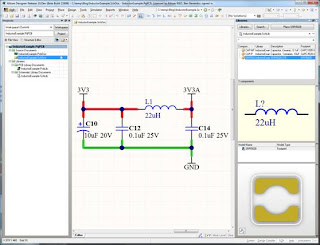

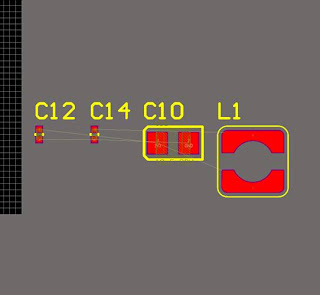

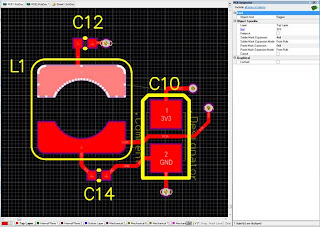

Improved handling of duplicate pad names on a PCB component (footprint)

Some power devices have thermal pads that require connection to Ground (GND). Because these pads are often left out of the component’s schematic symbol, an explicit GND connection can not be made. Instead, PCB Component (footprint) creators sometimes force a GND connection by designating thermal pads with the same name as another GND pad on the PCB Component. This creates a 1:many relationship between schematic pins and PCB Component pads which Update 14 handles much better by ensuring that net connectivity is correctly established across all designated pads, regardless of whether they contain duplicated names.

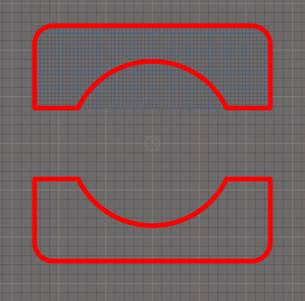

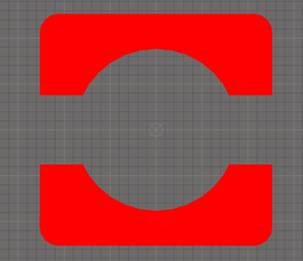

Smoother cycling between designated routing layers

Altium Designer has long supported DRC rules to limit the layers that a net can be routed on. While these rules are checked and flagged as part of the DRC process, Altium Designer did not actively prevent illegal routes from being made during interactive routing. This latest update adds an additional layer of rule protection by ensuring that designers can only select layers permitted by the design rules during interactive routing; even if prohibited layers are also visible.

In total, 11 BugCrunch items have been included in this latest update, along with various other enhancements, with the full information listed in the release notes.

The delivery of this update affects the following 12 modules:

- System Components category: Altium Designer Base, PCB System, Schematic System, Soft Design Support

- Importers and Exporters category: Exporter - AutoCAD DWG, Exporter - DXF, Exporter - Hyperlynx, Importer - Allegro, Importer - PADS

- Output Generators category: Output - Gerber, Output - NC-Drill, Output - Gerber

This is the first release since the introduction of the patching system in Update 13. You should see a dramatic reduction in the size of the download required to install this update, and future ones, compared with previous updates. For example, the total download for Update 14 under the new system is 11MB, instead of 84MB which would have been experienced under the previous update system. Note though, the patching system works on your download cache so if you have cleared the cache since installing, it will require some modules (or all, depending on when you did it) to update using the previous update system, thus applying the full update to these modules.

Installation of the updated modules will bring their revision up to 10.771.23139. The Platform Build number will also update to 10.771.23139 as the Altium Designer Base module is updated.

To update your Altium Designer 10 installation, ensure you are using a license with valid subscription. Go to the Plug-in page (DXP >> Plug-ins and Updates) and select “Update All”. If you don’t see the update, use the “Refresh” link in top right hand corner of the Plugins page.

Note: If you are using a Private Server license or Standalone license, and you have renewed your subscription since activation, you will be required to reactivate your license to obtain this and future updates.

For those who installed directly from DVD, you can access the updates by changing a setting in preferences: System >> Installation Manager, change the Remote Repository Location to http://installation.altium.com

If you are wanting to install a new build containing this update, please download the latest Installer/Uninstaller to support this build.